SZJLD-288型 计算机组成原理• 微机原理与接口技术综合实验装置

一、产品简介:

“SZJLD-288型计算机组原理• 微机原理与接口技术综合实验装置”适用于大中专院校计算机微机综合型课程教学实验与技能实训考核的理想计算机教学设备。

二、实验台桌:

中瓯牌实验台由铝木结构,采用特制模具制作的优质铝合金做框架,铝合金表面经氧化处理,经久耐用,美观大方,符合现代审美观,桌面为防火、防水、耐磨高密度板,桌子下部配置储存柜及电脑主机柜。

三、系统组成:

A、微机原理与接口技术部分:

1、硬件概述:

中瓯牌微机原理与接口技术教学实验系统采用Intel 8086/8088微处理器作为系统核心,全面支持80X86的16位微机原理与接口技术的实验教学,为16位微处理器在微机教学中的运用构建了一个全开放、可开发、易拓展式的实验环境。

2、软件概述:

系统配有MKStudio集成开发环境,支持32/64位的Win XP~Win10操作系统,支持80X86汇编语言和C语言的源程序级编程与调试,支持寄存器、内存和外设接口芯片的非编程读写操作,支持常用的INT 21h功能调用,支持脱机模拟调试。

3、总线特性:

系统开放了总线宽度的动态选择机制,把总线宽度控制“BS8”列入用户可定义的范围,为了简化电路连接,系统对该输入信号的缺省定义为“16位”,即当用户扩展16位存储器或输入输出接口时可忽略对“BS8”的定义与连接。

4、寻址能力:

系统构建了全覆盖的寻址空间,系统内存可融入仼意段的0~1FFFh,可寻址范围为16个段的0~1FFFh(其中F000为系统BIOS段),当IP大于等于2000h时,系统的寻址目标指向外部存储器扩展空间。系统对于I/O的扩展寻址无制约,0~FFFFh共64K全空间开放。

5、扩展能力:

系统的内存和I/O扩展以字节操作为基准,把高低字节允许信号BHE、BLE列入扩展定义的范围,支持字与字节指令的扩展寻址,并把DMA操作期间的字节定义融入到BHE、BLE选通端,使其扩展特性与微机实际应用无缝结合。

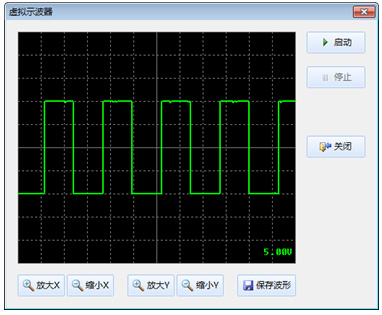

6、虚拟仪器:

系统集成了虚拟示波器、虚拟电压表功能,可测量实验中实际产生的模拟信号、数字信号,通过PC软件显示波形和电压值,支持波形X-Y缩放,并可将波形保存为BMP图片用于实验报告。

7、连线方式:

系统提供了扁平线、排线和单线相结合的电路连线方式:数据总线、地址总线、控制总线及8芯以上的接口采用扁平连接或排线连接;读写控制、选通端采用单线连接,进一步优化了电路的搭接方式,提高了电路的连接效率。

8、安全特性:

系统引出的扩展总线均由隔离器件驱动,“隔离”设计保障了16位微处理核的安全,避免了误操作、误连线对CPU造成的损伤;“驱动”设计的目的提高了系统扩展总线的稳定性和可靠性。另外系统内置了具有短路保护、过流保护的高性能稳压开关电源,进一步保障了系统的安全性。

★ 微机实验项目:

(一)微机原理实验:

1、系统认识实验

2、数制转换实验

◆ 十六进制数转换为十进制数

◆ 十进制数转换为十六进制数

3、码制转换实验

◆ ASCII码(数字符)转换为十六进制数

◆ 十六进制数转换为ASCII码

◆ ASCII码(数字符)转换为十进制数

◆ 十进制数转换为ASCII码

◆ 十进制数的ASCII码转换为BCD码

◆ 十进制BCD码转换为二进制数

4、运算类编程实验

◆ 二进制双精度加法运算

◆ 十进制的BCD码减法运算

◆ 乘法运算

5、分支程序设计实验

6、循环程序设计实验

◆ 计算S=1+2×3+3×4+4×5+…+N(N+1)

◆ 求某数据区内负数的个数

7、排序程序设计实验

◆ 气泡排序法

◆ 学生成绩名次表

8、子程序设计实验

◆ 求无符号字节序列中的Z大值和Z小值

◆ 求N!

9、查表程序设计实验

10、INT 21h输入输出程序设计实验

◆ 显示A~Z共26个大写英文字母

◆ INT 21H功能调用示例程序实验

◆ 在C语言使用INT 21h功能调用

◆ PC键盘下传实验箱七段码显示

◆ 实验箱键盘上传PC屏幕显示

(二)微机接口实验项目:

1、存储器扩展实验

2、8259中断控制器实验

◆ 8259单级中断控制

◆ 8259多级中断控制

3、I/O扩展实验(8位/16位)

4、8255并行口实验

◆ 8255 A/B/C口输出方波

◆ 8255 PA输入/PB输出

◆ 8255控制交通灯

5、8253定时/计数器应用实验

6、8251串行通信应用实验

7、键盘扫描及显示设计实验

◆ 8279键盘与显示设计

◆ 8255键盘与显示设计

8、8237可编程DMA控制器实验

9、A/D模数转换实验

10、D/A数模转换实验

11、LCD 128×64图形液晶实验

12、LED 16×16点阵显示实验

13、音频驱动实验

14、继电器控制实验

15、步进电机控制实验

16、直流电机调速实验

17、DS18B20数字温度传感器实验

18、V/F电压频率转换实验

19、PWM输出实验

20、DS1302实时时钟

21、红外遥控实验

22、电子琴实验

(三)32位汇编语言程序设计实验项目:(软件模拟运行)

1、32位数据排序实验

2、32位码制转换实验

3、32位存储器访问实验

B、计算机组成原理部分:

1、 系统概述

该现代计算机组成原理与系统结构是以广受赞誉的经典产品CMH+为基础研制的第三代面向教学实践领域的计算机应用类实验系统。该系统字长16位,具有16位数据总线、16位地址总线,可寻址64KB内存空间,并支持字、字节操作。

2、体系结构

系统可按通用计算机的标准设计原理计算机,把模型机的构造特性与8086/8051相兼容。系统对于“定长指令”仅从指令格式分类的角度举例验正,动态的体系结构彻底摆脱了非标准实验环境下特定和虚构的不规范语言给原理计算机语言教学实践活动所带来的困扰。

3、 指令构造

该的指令格式采用“变长指令字”结构,不同指令操作码不完全相同,操作码的位数不固定,结构灵活,减少指令码冗余,提高执行效率,能充分利用指令码所有位,Z多可以设计256条指令。在通用汇编器的支撑下,既可设计属于您自己的个性化指令系统,亦可设计成与16/8位微处理器兼容的标准指令系统,为模型计算机的通用化设计构建了一个可操作平台。

4、 微控制器

该运用“PLA”理念,用存储器逻辑与组合逻辑相结合的方法构造微控制器,根据程序需要自动变更当前控制逻辑,对于使用频率高的简单指令以及很有用又不复杂的指令选择组合逻辑,遇复杂的、不规整需扩充的指令选择存储器逻辑,从而实现动态计算机体系结构。

5、 后续微址

微程序控制器中隐含后续微地址(BAF),采用断定法,由转移控制段BCF(2位)规定后续微地址形成方式,支持顺序执行(uPC+1),进位位转移,零标志转移,无条件转移,在取指周期以操作码形成后续微地址。

6、 时序层次

该拥有一个周期、节拍、脉冲组成的三级时序系统。以取指周期为始设了四个状态触发器,在组合逻辑控制中,该触发器为1,控制器进入那个机器周期的微操作。系统按序定拍,随机器周期动态变更节拍发生器,在非取指周期产生T1→T3→T4三拍制节拍发生器,在取指周期产生T1→T2→T3→T4四拍制发生器。

7、 卓越的软硬件环境

实时部件显示:各部件单元都以计算机结构模型布局,清晰明了,各部件均有七段数码管显示其十六进制内容。两个数据流方向指示灯以直观反映当前数据的来源与目标去向。即使不借助PC机也可实时观察数据流状态,判断其正确性,提供一目了然的实验环境。

开放式设计:系统支持三种实验电路构造方式,即实验单元电路的硬布线连接方式、单元电路的控位连接方式和实验电路“软连线”方式。对于实验单元电路的硬布线连接方式,可采用双头实验导线从零开始在扩展区域逐一搭起一个实验电路;对于各单元电路的控位连接,只需使用双头实验导线在单元电路控位与控制信号之间对应连接,就可构造出实验所需的部件控制电路;亦可使用可编程逻辑器件在线设计下载实验电路,实现实验电路的“软接线”。

逻辑分析:对于教师而言,不难体会要讲清时序关系是不容易的,而学生理解并利用时序关系则难上加难。而由于现代集成技术的迅猛发展,在实际工作中需要更多的利用逻辑分析工具进行时序分析。达爱思计算机组成原理教学实验系统具备逻辑分析功能,老师可通过电化教学设备向学生现场展示指令与时序的关系,让学生在实验时直观地观测到指令与时序的关系,有效的提高教学效果。

8、 灵活的多操作方式

该以高性能MCU为核心组成系统的操作与控制平台,自带键盘、LCD显示,配备强大的集成开发环境,拥有前后台双环境支持,跟踪运行轨迹、受理中断请求、变更控制模式、捕捉现场信息。

9、 主流处理器的多总线结构

系统采用多总线结构,分别是数据总线、指令总线、微总线。这种三者分离并行的总线结构,遇取指周期可以并行完成操作数的存取,在当前指令结束后的首个微周期可直接进入下一条指令的取指操作,通过微总线形成电路解释与执行的后续微址,因此指令总线与微总线的主要仼务是预取指与后续微址的预处理。

10、 FPGA开发支持,提供所有VHDL例程

系统可选配Xilinx的XCV200扩展板,具有20万门大规模FPGA用于CPU模型的设计,16位64K的RAM用于存放用户程序及数据。学生将设计好的CPU模型下载到FPGA,并将需要运行的程序下载到RAM,根据先易后难的实践思路逐步完成16位机、32位机的设计。

★ 计算机实验项目:

(一) 单元实验项目:

1、运算器实验

2、通用寄存器实验

3、准双向I/O口实验

4、地址总线组成实验

5、十六位数据总线实验

6、存储器读写实验

7、指令总线运用实验

8、中断控制实验

9、微控制器实验

10、时序部件实验

(二)模型机及硬布线控制器实验:

1、基本模型机的设计与实现

2、分段模型机的设计与实现

3、带移位运算的模型机的设计与实现

4、复杂模型机的设计与实现

5、流水模型机的设计与实现

6、基于RISC处理器构成模型机实验

7、基于重叠技术构成的模型机实验

8、中断模型机的设计与实现

9、PLA综合模型机的设计与实现

(三)通用计算机实验:

1、MCS-51单片机的设计与实现

2、8086微处理器的设计与实

客服1

客服1